PIA 6821 2個搭載パラレルI/O基板 完成品 [PIA6821-ERIS-FP]

PIA 6821 2個搭載パラレルI/O基板 完成品

[PIA6821-ERIS-FP]

販売価格: 17,000円(税別)

(税込: 18,700円)

在庫数 3

商品詳細

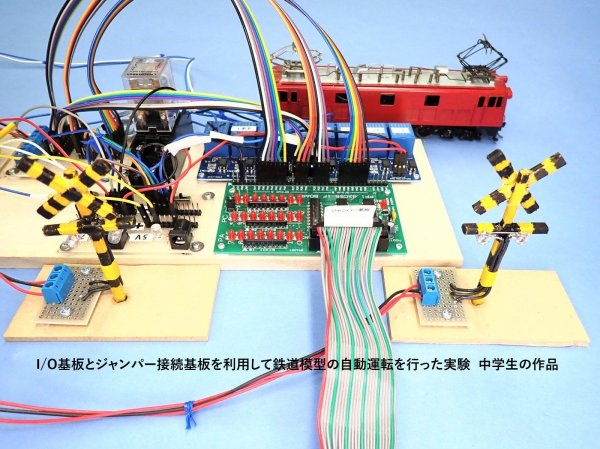

8bitマイコンの面白さは、I/O機能を利用した外部機器制御です。

高度なオペレーティングシステムを持たない8bitマイコンは、APIを利用する事無く、外部機器を簡単に直接制御できます。

手軽に外部機器の制御を楽しんでいただける様に、多彩なI/O基板をご用意しました。

PIA 6821 2個搭載 パラレルI/O基板のご説明

6800系CPU用に開発された標準的なパラレルインターフェースLSI「PIA6821」を2個搭載したパラレルインターフェースカードです。

PIAの意味は、Peripheral Interface Adapter です。

6800系のCPUバスに接続する仕様ですが、問題無く6502系のCPUバスに接続して利用できます。

PIA基板は、基板上のCPU設定ジャンパーピンを切り替える事で、ERIS6800 CPU基板、ERIS6502 CPU基板(8MHz動作)の両方に対応できます。

PIA6821は、8bitパラレルインターフェースと2本の制御信号線を持つI/Oポートを2セットを内蔵しています。

2本の制御信号線は、パラレル信号のストローブ信号や、ハンドシェーク制御用として利用できます。

基板上のアドレス設定ジャンパーピンを切り替える事で、ERIS6800、ERIS6502 CPU基板に2枚の「PIA6821-6800-FP」基板を実装できます。

26Pフラットケーブルで、ジャンパー基板と接続して、ブレイクアウト基板としてブレッドボード等に組んだ回路と接続できます。

ERIS6800、ERIS6502は、同じ種類のI/Oインターフェース基板を最大2枚まで増設できます。

ERIS6800、ERIS6502は、異なる種類のI/Oインターフェース基板を最大4枚まで増設できます。

増設例:1

・PPI 8255 パラレルI/O基板 アドレス設定 1

・PPI 8255 パラレルI/O基板 アドレス設定 2

・PIA 6821 パラレルI/O基板

・VIA 6522 パラレルI/O基板

増設例:2

・PIA 6821 パラレルI/O基板 アドレス設定 1

・PIA 6821 パラレルI/O基板 アドレス設定 2

・PPI 8255 パラレルI/O基板

・VIA 6522 パラレルI/O基板

増設例:3

・VIA 6522 パラレルI/O基板 アドレス設定 1

・VIA 6522 パラレルI/O基板 アドレス設定 2

・PPI 8255 パラレルI/O基板

・PIA 6522 パラレルI/O基板

増設例:4

・PPI 8255 パラレルI/O基板 アドレス設定 1

・PPI 8255 パラレルI/O基板 アドレス設定 2

・PIA 6821 パラレルI/O基板 アドレス設定 1

・PIA 6821 パラレルI/O基板 アドレス設定 2

ERIS6800、ERIS6502の最大構成では、パラレルI/O基板 4枚 + MAI基板 1枚の合計5枚の基板を増設できます。

最大構成例

・PPI 8255 パラレルI/O基板 アドレス設定 1

・PPI 8255 パラレルI/O基板 アドレス設定 2

・PIA 6821 パラレルI/O基板

・VIA 6522 パラレルI/O基板

・MAI基板 メモリ・アクセス・インジケーター

入出力コネクタ:26ピンコネクタで8biit ポート x3個と電源線を接続します。

ERIS6800用インターフェース基板間で共通仕様になっています。

実験に便利な、ジャンパー接続基板(ブレイクアウト端子)を用意しています。

Legacy8080の26ピンI/Oコネクタと互換性があります。

実装PIAの仕様:6821互換品のPIAを実装します。PIAの製造メーカーや型番の指定はできません。

・PIA 6821 パラレルI/O基板の大きさ 横幅:10cm、奥行:6.5cm、高さ:3cm (突起部含む)

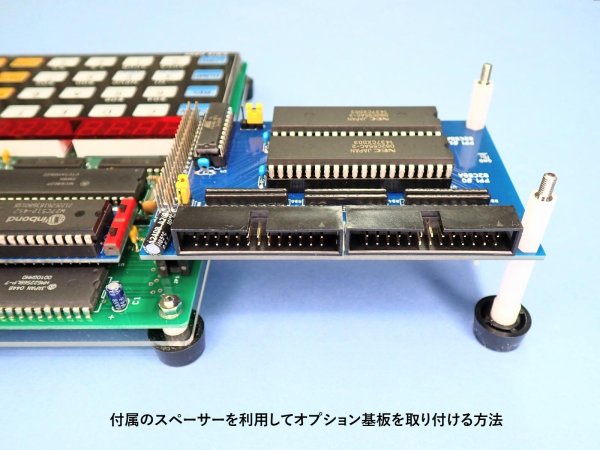

付属品

・I/O基板、周辺基板を重ねて実装するためのスペーサー 2個

・スタック接続コネクタピンの保護カバー(緑色) 1個

・PDF版のマニュアル

(初期に付属するのは暫定版のマニュアルになります。正式版が完成しだい配布します。)

納期

・購入ボタン(カートに入れるボタン)そばに、在庫表示が有る場合の標準納期は、ご注文(お支払い確認)より1週間です。

・完成品が在庫切れになると、自動的に「受注生産」表示に切り替わります。

・購入ボタン(カートに入れるボタン)そばに、受注生産の表示が有る場合は、納期に4週間ほどかかる場合があります。

・正確な納期は、ご注文後にご連絡いたします。

その他事項

・本製品の仕様、販売価格を予告なく変更する場合があります

高度なオペレーティングシステムを持たない8bitマイコンは、APIを利用する事無く、外部機器を簡単に直接制御できます。

手軽に外部機器の制御を楽しんでいただける様に、多彩なI/O基板をご用意しました。

PIA 6821 2個搭載 パラレルI/O基板のご説明

6800系CPU用に開発された標準的なパラレルインターフェースLSI「PIA6821」を2個搭載したパラレルインターフェースカードです。

PIAの意味は、Peripheral Interface Adapter です。

6800系のCPUバスに接続する仕様ですが、問題無く6502系のCPUバスに接続して利用できます。

PIA基板は、基板上のCPU設定ジャンパーピンを切り替える事で、ERIS6800 CPU基板、ERIS6502 CPU基板(8MHz動作)の両方に対応できます。

PIA6821は、8bitパラレルインターフェースと2本の制御信号線を持つI/Oポートを2セットを内蔵しています。

2本の制御信号線は、パラレル信号のストローブ信号や、ハンドシェーク制御用として利用できます。

基板上のアドレス設定ジャンパーピンを切り替える事で、ERIS6800、ERIS6502 CPU基板に2枚の「PIA6821-6800-FP」基板を実装できます。

26Pフラットケーブルで、ジャンパー基板と接続して、ブレイクアウト基板としてブレッドボード等に組んだ回路と接続できます。

ERIS6800、ERIS6502は、同じ種類のI/Oインターフェース基板を最大2枚まで増設できます。

ERIS6800、ERIS6502は、異なる種類のI/Oインターフェース基板を最大4枚まで増設できます。

増設例:1

・PPI 8255 パラレルI/O基板 アドレス設定 1

・PPI 8255 パラレルI/O基板 アドレス設定 2

・PIA 6821 パラレルI/O基板

・VIA 6522 パラレルI/O基板

増設例:2

・PIA 6821 パラレルI/O基板 アドレス設定 1

・PIA 6821 パラレルI/O基板 アドレス設定 2

・PPI 8255 パラレルI/O基板

・VIA 6522 パラレルI/O基板

増設例:3

・VIA 6522 パラレルI/O基板 アドレス設定 1

・VIA 6522 パラレルI/O基板 アドレス設定 2

・PPI 8255 パラレルI/O基板

・PIA 6522 パラレルI/O基板

増設例:4

・PPI 8255 パラレルI/O基板 アドレス設定 1

・PPI 8255 パラレルI/O基板 アドレス設定 2

・PIA 6821 パラレルI/O基板 アドレス設定 1

・PIA 6821 パラレルI/O基板 アドレス設定 2

ERIS6800、ERIS6502の最大構成では、パラレルI/O基板 4枚 + MAI基板 1枚の合計5枚の基板を増設できます。

最大構成例

・PPI 8255 パラレルI/O基板 アドレス設定 1

・PPI 8255 パラレルI/O基板 アドレス設定 2

・PIA 6821 パラレルI/O基板

・VIA 6522 パラレルI/O基板

・MAI基板 メモリ・アクセス・インジケーター

入出力コネクタ:26ピンコネクタで8biit ポート x3個と電源線を接続します。

ERIS6800用インターフェース基板間で共通仕様になっています。

実験に便利な、ジャンパー接続基板(ブレイクアウト端子)を用意しています。

Legacy8080の26ピンI/Oコネクタと互換性があります。

実装PIAの仕様:6821互換品のPIAを実装します。PIAの製造メーカーや型番の指定はできません。

・PIA 6821 パラレルI/O基板の大きさ 横幅:10cm、奥行:6.5cm、高さ:3cm (突起部含む)

付属品

・I/O基板、周辺基板を重ねて実装するためのスペーサー 2個

・スタック接続コネクタピンの保護カバー(緑色) 1個

・PDF版のマニュアル

(初期に付属するのは暫定版のマニュアルになります。正式版が完成しだい配布します。)

納期

・購入ボタン(カートに入れるボタン)そばに、在庫表示が有る場合の標準納期は、ご注文(お支払い確認)より1週間です。

・完成品が在庫切れになると、自動的に「受注生産」表示に切り替わります。

・購入ボタン(カートに入れるボタン)そばに、受注生産の表示が有る場合は、納期に4週間ほどかかる場合があります。

・正確な納期は、ご注文後にご連絡いたします。

その他事項

・本製品の仕様、販売価格を予告なく変更する場合があります